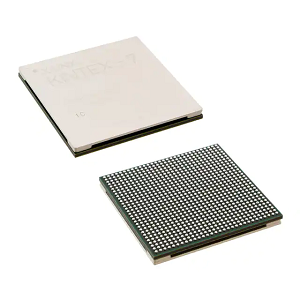

XC7K420T-2FFG901I – Integrirana vezja, vdelana, s polja programabilna polja vrat

Lastnosti izdelka

| VRSTA | ILUSTRACIJ |

| kategorijo | Integrirana vezja (IC)Vdelano Field Programmable Gate Arrays (FPGA) |

| proizvajalec | AMD |

| serije | Kintex®-7 |

| zaviti | pladenj |

| Stanje izdelka | Aktiven |

| DigiKey je programabilen | Ni preverjeno |

| LAB/CLB številka | 32575 |

| Število logičnih elementov/enot | 416960 |

| Skupno število bitov RAM | 30781440 |

| Število V/I | 380 |

| Napetost - Napajanje | 0,97 V ~ 1,03 V |

| Vrsta namestitve | Tip površinskega lepila |

| Delovna temperatura | -40°C ~ 100°C (TJ) |

| Paket/ohišje | 900-BBGA, FCBGA |

| Enkapsulacija komponente proizvajalca | 901-FCBGA (31x31) |

| Glavna številka izdelka | XC7K420 |

| VRSTA | ILUSTRACIJ |

| kategorijo | Integrirana vezja (IC)Vdelano |

| proizvajalec | AMD |

| serije | Kintex®-7 |

| zaviti | pladenj |

| Stanje izdelka | Aktiven |

| DigiKey je programabilen | Ni preverjeno |

| LAB/CLB številka | 32575 |

| Število logičnih elementov/enot | 416960 |

| Skupno število bitov RAM | 30781440 |

| Število V/I | 380 |

| Napetost - Napajanje | 0,97 V ~ 1,03 V |

| Vrsta namestitve | Tip površinskega lepila |

| Delovna temperatura | -40°C ~ 100°C (TJ) |

| Paket/ohišje | 900-BBGA, FCBGA |

| Enkapsulacija komponente proizvajalca | 901-FCBGA (31x31) |

| Glavna številka izdelka | XC7K420 |

FPGA

Prednosti

Prednosti FPGA so naslednje:

(1) FPGA so sestavljeni iz virov strojne opreme, kot so logične celice, RAM, množilniki itd. Z racionalno organizacijo teh virov strojne opreme je mogoče implementirati strojna vezja, kot so množilniki, registri, generatorji naslovov itd.

(2) FPGA je mogoče oblikovati z uporabo blokovnih diagramov ali Verilog HDL, od preprostih vratnih vezij do FIR ali FFT vezij.

(3) FPGA je mogoče neskončno reprogramirati, naložiti novo oblikovno rešitev v samo nekaj sto milisekundah, z uporabo rekonfiguracije za zmanjšanje stroškov strojne opreme.

(4) Delovno frekvenco FPGA določata čip FPGA in zasnova ter jo je mogoče spremeniti ali nadomestiti s hitrejšim čipom, da izpolni določene zahtevne zahteve (čeprav delovna frekvenca seveda ni neomejena in lahko povečati, vendar ga urejajo trenutni procesi IC in drugi dejavniki).

Slabosti

Slabosti FPGA so naslednje:

(1) FPGA se zanašajo na izvedbo strojne opreme za vse funkcije in ne morejo izvajati operacij, kot so razvejani pogojni skoki.

(2) FPGA lahko izvajajo samo operacije s fiksno točko.

Če povzamemo: FPGA se zanašajo na strojno opremo za izvajanje vseh funkcij in jih je mogoče primerjati z namenskimi čipi v smislu hitrosti, vendar obstaja velika vrzel v prilagodljivosti načrtovanja v primerjavi s procesorji za splošne namene.

Oblikovalski jeziki in platforme

Programabilne logične naprave so nosilci strojne opreme, ki s tehnologijo EDA konkretizirajo uveljavljene funkcije in tehnične specifikacije elektronskih aplikacij.FPGA, kot ena izmed glavnih naprav, ki izvajajo to pot, so neposredno usmerjeni k uporabniku, izjemno prilagodljivi in vsestranski, enostavni za uporabo ter hitri za testiranje in implementacijo v strojno opremo.

Jezik za opis strojne opreme (HDL) je jezik, ki se uporablja za načrtovanje digitalnih logičnih sistemov in opis digitalnih vezij, glavna pogosto uporabljena so VHDL, Verilog HDL, System Verilog in System C.

Kot vsestranski opisni jezik strojne opreme ima jezik za opis strojne opreme zelo hitrega integriranega vezja (VHDL) značilnosti, da je neodvisen od specifičnega vezja strojne opreme in neodvisen od platforme zasnove, s prednostmi zmožnosti opisovanja širokega spektra, ne odvisno od določenih naprav in zmožnost opisa zasnove kompleksne krmilne logike v strogi in jedrnati kodi itd. Podpirajo ga številna podjetja EDA in se pogosto uporablja na področju elektronskega načrtovanja.za široko uporabo.

VHDL je jezik na visoki ravni za načrtovanje vezij in ima v primerjavi z drugimi opisnimi jeziki strojne opreme značilnosti enostavnega jezika, prilagodljivosti in neodvisnosti od zasnove naprave, zaradi česar je običajen opisni jezik strojne opreme za tehnologijo EDA, zaradi česar je tehnologija EDA boljša. dostopen oblikovalcem.

Verilog HDL je široko uporabljen opisni jezik strojne opreme, ki se lahko uporablja v več fazah procesa načrtovanja strojne opreme, vključno z modeliranjem, sintezo in simulacijo.

Verilog HDL Prednosti: podoben C, enostaven za učenje in prilagodljiv.Razlikuje med velikimi in malimi črkami.Prednosti pri pisanju dražljajev in modeliranja.Slabosti: veliko napak ni mogoče zaznati med prevajanjem.

Prednosti VHDL: stroga sintaksa, jasna hierarhija.Slabosti: dolg čas uvajanja, premalo prilagodljiv.

Programska oprema Quartus_II je popolno okolje za načrtovanje z več platformami, ki ga je razvila Altera, ki lahko zadovolji potrebe po načrtovanju različnih FPGA in CPLD ter je celovito okolje za načrtovanje sistemov, ki jih je mogoče programirati na čipu.

Vivado Design Suite, integrirano načrtovalsko okolje, ki ga je leta 2012 izdal prodajalec FPGA Xilinx. Vključuje visoko integrirano načrtovalsko okolje in novo generacijo orodij od sistemske do IC ravni, vsa zgrajena na skupnem razširljivem podatkovnem modelu in skupnem okolju za odpravljanje napak.Xilinx Vivado Design Suite ponuja jedra FIFO IP, ki jih je mogoče preprosto uporabiti pri dizajnih.